- 全部

- 默认排序

一个学习信号完整性仿真的layout工程师做layout工程师都知道差分等长规则的设置,但可能有的不了解Xnet的设置,因为在我们平常的layout中发现,其实在电阻或者电容的另一端的走线是特别短的,如果要求没那么严格,也就不需要设置Xne

一个layout工程师学习信号完整性之路串扰还是比较复杂的一个东西,在工作中好多人询问串扰仿真怎么分析,其实对于仿真流程相对简单,但是真正利用这个仿真去做优化的相对较少,所以还是要理解其中的原理,在layout中去设计,比如常说的3W等,也

一个学习信号完整性仿真的layout工程师因为每个人的习惯不同,所以在平常的设计中查看的光绘层是不同的,有助于自己快速的layout。但是在每次拿到别人的板子去改版或者重新设计时,都要添加自己习惯的光绘层,就比较麻烦。每次都要新建相应显示层

一个layout工程师学习信号完整性之路造成电源完整性的问题有很多,之前也和大家分享过一些。但这些问题都不是独立的,他们之间的原理是互通,可能解决了这个问题另外一个问题就解决了。可能对于这个SSN在我们实际的LAYOUT或者测试工程师接触的

一个layout工程师学习信号完整性之路在工作中经常会遇到有人问什么是高速电路,或者在设计高速电路的时候需要注意什么。每当遇到这种问题就头脑发懵,其实不同的产品、不同的人对其都有不同的理解。今天简单总结一下最基本的一些概念包括对高速电路的理

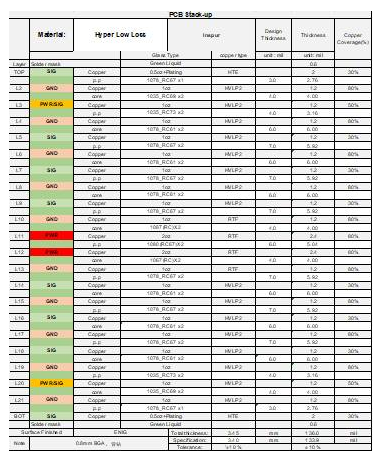

PCB板卡作为交换机硬件架构的重要组成部分,承载着各种硬件器件和部件,其可靠性至关重要,直接影响交换机的整体性能。随着数据中心的快速发展,交换机单lane信号速率也在飞速提升,这对PCB和SI设计而言都是全新的挑战。本文将从PCB的硬件设计

近年来,随着“内卷化”一词的火速出圈,我们仿佛进入了一个“万物皆可内卷”的时代,教育内卷化、行业内卷化、职场内卷化....所谓的“内卷化”是指一种模式发展到一定阶段后停滞不前,无法进入更高阶段的一种现象。电子行业自然也不例外面临着“内卷化”

一个layout工程师学习信号完整性之路上一篇文章介绍IBIS的基本构造,下面简单整理IBIS中一些常用的概念,以便于我们在使用IBIS知道这些都代表什么意思:IBIS中术语解释R_pkg、L_pkg、C_pkg:封装参数C_comp:为硅

一个layout工程师学习信号完整性之路本人最早接触SI仿真的时候,只是进行一个简单的流程操作,其中涉及到的原理、模型知之甚少,再后来慢慢的接触到了深一点的东西开始自己搭建电路了解到了IBIS。用于电路仿真的模型有好多,可能IBIS是最常用

一个layout工程师学习信号完整性之路最近在进行信号完整性仿真的仿真时,被人问到的码型是什么样子,一下子就有点懵了。发现自己的盲区有多了一块,码型是什么东西?所以上网收集整合了一些资料,发现这些东西都是平常自己用到的,只不过没有在意。下面

扫码关注

扫码关注